- 您现在的位置:买卖IC网 > Sheet目录1220 > HW-USB-II-G (Xilinx Inc)PLATFORM CABLE USB II

�� �

�

�

�Platform� Cable� USB� II�

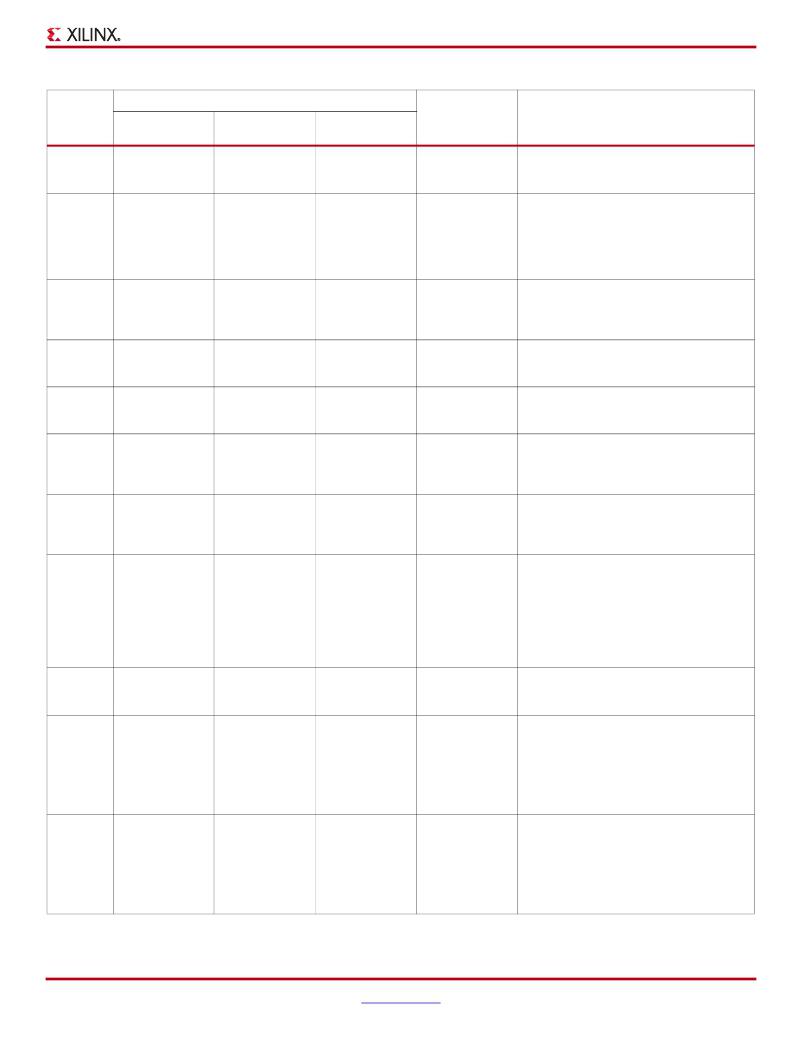

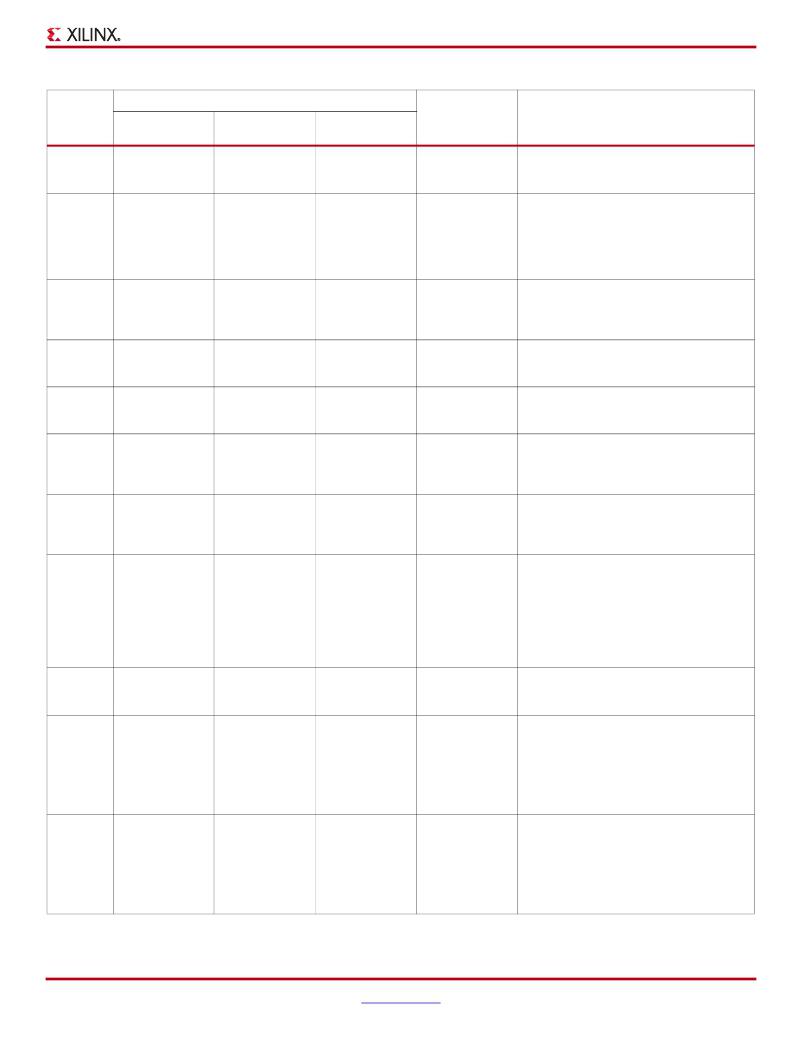

�Table� 6:� JTAG/SPI/Slave� Serial� Port:� 2-mm� Connector� Signals� (Cont’d)�

�Pin�

�Number�

�JTAG�

�Configuration�

�MODE�

�SPI�

�Programming� (1)�

�Slave-Serial�

�Configuration�

�Direction� (2)�

�Description�

�JTAG� Test� Data� In� .� This� pin� outputs� the�

�10�

�TDI�

�–�

�–�

�Out�

�serial� data� stream� transmitted� to� the� TDI� pin�

�on� the� first� device� in� a� JTAG� chain.�

�JTAG� Pseudo� Ground.� Use� of� this� pin� is�

�optional.� PGND� is� pulled� Low� during� JTAG�

�13�

�PGND�

�–�

�–�

�Out�

�operations;� otherwise,� it� is� high-Z.� This� pin� is�

�connected� to� an� open-drain� driver� and�

�requires� a� pull-up� resistor� on� the� target�

�system.� (4)�

�JTAG� Halt.� Use� of� this� pin� is� optional.� Host�

�14�

�HALT�

�–�

�–�

�Out�

�applications� can� customize� the� behavior� of�

���SPI� Select� .� This� pin� is� the� active-Low� SPI�

�4�

�–�

�SS�

�–�

�Out�

�chip� select� signal� and� should� be� connected�

�to� the� S� (1)� pin� on� the� SPI� flash� device.�

�SPI� Clock� .� This� pin� is� the� clock� signal� for�

�6�

�–�

�SCK�

�–�

�Out�

�SPI� operations� and� should� be� connected� to�

�the� C� (1)� pin� on� the� SPI� flash� PROM.�

�SPI� Master-Input,� Slave-Output� .� This� pin�

�8�

�–�

�MISO�

�–�

�In�

�is� the� target� serial� output� data� stream� and�

�should� be� connected� to� the� Q� (1)� pin� on� the�

�SPI� flash� device.�

�SPI� Master-Output� Slave-Input� .� This� pin�

�10�

�–�

�MOSI�

�–�

�Out�

�outputs� the� target� serial� input� data� stream�

�for� SPI� operations� and� should� be� connected�

�to� the� D� (1)� pin� on� the� SPI� flash� device.�

�SPI� Pseudo� Ground� .� PGND� is� pulled� Low�

�during� SPI� operations;� otherwise,� it� is� high-�

�Z.� When� connected� to� PROG_B� on� an�

�13�

�–�

�PGND�

�–�

�Out�

�FPGA,� the� FPGA� will� high-Z� its� SPI� signals�

�while� the� cable� is� programming� the� SPI�

�flash.� This� pin� is� connected� to� an� open-drain�

�driver� and� requires� a� pull-up� resistor� on� the�

�target� system.� (4)�

�SPI� Write� Protect� .� This� pin� is� reserved� for�

�14�

�–�

�WP�

�–�

�–�

�future� use.� Do� not� connect� for� SPI�

�programming.�

�Slave� Serial� Configuration� Reset� .� This� pin�

�is� used� to� force� a� reconfiguration� of� the�

�target� FPGA(s)� and� should� be� connected� to�

�4�

�–�

�–�

�PROG�

�Out�

�the� PROG_B� pin� of� the� target� FPGA� for� a�

�single-device� system,� or� to� the� PROG_B� pin�

�of� all� FPGAs� in� parallel� in� a� daisy-chain�

�configuration.�

�Slave� Serial� Configuration� Clock� .� FPGAs�

�load� one� configuration� bit� per� CCLK� cycle� in�

�Slave� Serial� mode.� CCLK� should� be�

�6�

�–�

�–�

�CCLK�

�Out�

�connected� to� the� CCLK� pin� on� the� target�

�FPGA� for� single-device� configuration,� or� to�

�the� CCLK� pin� of� all� FPGAs� in� parallel� in� a�

�daisy-chain� configuration.�

�DS593� (v1.2.1)� March� 17,� 2011�

��30�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

HW-USBN-2A

ACCY USB DOWNLOAD CABLE STD SPD

HW-V4-ML401-USA

EVALUATION PLATFORM VIRTEX-4

HW-V4-ML423-UNI-G

EVALUATION PLATFORM VIRTEX-4

HW-V4SX35-VIDEO-SK-UK

VIRTEX-4 VIDEO STARTER KIT

HW-V5-ML521-UNI-G

EVALUATION PLATFORM VIRTEX-5

HW-XA3S1600E-UNI-G

KIT DEVELOPMENT AUTOMOTIVE ECU

HW-XGI-VIDEO-US

DAUGHTER CARD VIDEO I/O VIODC

ICD15S13E6GV00LF

CONN DSUB HD SOCKT 15POS R/A PCB

相关代理商/技术参数

HW-USBN-2A

功能描述:程序设计器配件 ispDOWNLOAD Cable RoHS:否 制造商:Lattice 产品:ispDOWNLOAD Cables 用于:In-system Programming

HW-USBN-2B

功能描述:Lattice Programmable Products ispDOWNLOAD? In-System Programmer 制造商:lattice semiconductor corporation 系列:ispDOWNLOAD? 零件状态:有效 类型:系统内编程器 配套使用产品/相关产品:Lattice 可编程产品 内容:编程器 标准包装:1

HW-UW 30

制造商:OK International (OKI) / Metcal 功能描述:WRAPPING AND UNWRAPPING TOOL HAND 制造商:OK International (OKI) / Metcal 功能描述:WRAPPING AND UNWRAPPING TOOL, HAND

HW-UW-18-19

功能描述:手工工具 WRAP-UNWRAP TOOL, 18-19 AWG RoHS:否 制造商:Molex 产品:Extraction Tools 类型: 描述/功能:Extraction tool

HW-UW18-19

制造商:Jonard Industries 功能描述:WRAP-UNWRAP TOOL, 18-19 AWG

HW-UW-20

功能描述:手工工具 WRAP-UNWRAP TOOL, 20 AWG RoHS:否 制造商:Molex 产品:Extraction Tools 类型: 描述/功能:Extraction tool

HW-UW-224

功能描述:手工工具 WRAP-UNWRAP TOOL 22-24 A

RoHS:否 制造商:Molex 产品:Extraction Tools 类型: 描述/功能:Extraction tool

HW-UW-224-1

功能描述:手工工具 WRAP-UNWRAP TOOL, 22-24 AWG RoHS:否 制造商:Molex 产品:Extraction Tools 类型: 描述/功能:Extraction tool